Заземление точки схемы

При осуществлении заземления точки схемы её потенциал принимают равным нулю. Распределение токов при этом в схеме не меняется, потому что новые ветви, где могли бы протекать электрические токи, не образуются Подробнее

При осуществлении заземления точки схемы её потенциал принимают равным нулю. Распределение токов при этом в схеме не меняется, потому что новые ветви, где могли бы протекать электрические токи, не образуются Подробнее

Любые электрические цепи всегда подчиняются законам Кирхгофа.

Есть для первого закон Кирхгофа два варианта формулировок Подробнее

Под напряжение на участке электрической цепи имеется ввиду разность потенциалов на крайних точках участка Подробнее

Под напряжение на участке электрической цепи имеется ввиду разность потенциалов на крайних точках участка Подробнее

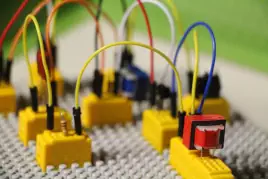

Электрические цепи можно поделить на разветвленные и неразветвленные. На рисунке ниже представлена схема неразветвленной электрической цепи в самом простом варианте Подробнее

Электрические цепи можно поделить на разветвленные и неразветвленные. На рисунке ниже представлена схема неразветвленной электрической цепи в самом простом варианте Подробнее

В теории электрических цепей любое электромагнитное устройство и физические процессы, которые происходят внутри него, а также в пространстве вокруг, заменяют на расчётный эквивалент.

В теории электрических цепей любое электромагнитное устройство и физические процессы, которые происходят внутри него, а также в пространстве вокруг, заменяют на расчётный эквивалент.

Электрической цепью называют нагрузки Подробнее

В элементах различных реально существующих электротехнических устройств происходят сложные процессы, связанные с протеканием токов смещения, токов проводимости, наведения ЭДС, выделения тепла, перераспределения и накопления энергии магнитного поля и электрического поля и прочее Подробнее

В элементах различных реально существующих электротехнических устройств происходят сложные процессы, связанные с протеканием токов смещения, токов проводимости, наведения ЭДС, выделения тепла, перераспределения и накопления энергии магнитного поля и электрического поля и прочее Подробнее

Электромагнитным полем называют такой особый вид материи, который характеризуется совокупностью электрического поля и магнитного поля, при этом они являются взаимосвязанными между собой и друг друга взаимообуславливают Подробнее

Электромагнитным полем называют такой особый вид материи, который характеризуется совокупностью электрического поля и магнитного поля, при этом они являются взаимосвязанными между собой и друг друга взаимообуславливают Подробнее

Электротехнические устройства подразделяют на:

Электротехнические устройства подразделяют на:

1. Генерирующие электрическую энергию (источники питания).

2. Использующие электрическую энергию (приёмники электроэнергии).

Приёмные устройства, подключённые к генерирующему устройству, образуют электрическую цепь Подробнее

В статье поле плоской пластины была выведена формула напряжённости электрического поля бесконечной плоской пластины. Если эту пластину рассмотреть в разрезе и ввести понятие поверхностной плотности заряда σ Подробнее

В статье поле плоской пластины была выведена формула напряжённости электрического поля бесконечной плоской пластины. Если эту пластину рассмотреть в разрезе и ввести понятие поверхностной плотности заряда σ Подробнее

Выполним расчёт электрического поля плоской пластины бесконечных размеров, которая заряжена с постоянной плотностью. В основу положим закон Кулона для взаимодействия 2-х точечных электрических зарядов в вакууме Подробнее

Выполним расчёт электрического поля плоской пластины бесконечных размеров, которая заряжена с постоянной плотностью. В основу положим закон Кулона для взаимодействия 2-х точечных электрических зарядов в вакууме Подробнее